## PERFORMANCE ANALYSIS OF 20 NM SI AND GE CHANNEL BASED PENTAGONAL AND TRAPEZOIDAL NWT

## JAIDEV, S.S. GILL, NAVNEET KAUR

Abstract: In this paper, we have investigated the variability in the performance of GAA FET (Gate All Around Field Effect Transistor) due to their cross section shapes and channel materials with the aid of 3D TCAD simulations. Pentagonal and trapezoidal Cross section shapes have been designed for constant diameter and height (10nm) with doped Si and Ge channel. The performance is evaluated in terms of Ion current, leakage current, switching speed, transfer and output characteristics, Drain Induced Barrier Lowering (DIBL), Subthreshold Swing (SS), threshold voltage (Vti) and compared with triangular NWT. After comparison, it shows that Si Pentagonal NWT structure is showing better performance i.e. high on-current, low DIBL and Low SS. Ge NWT offer better leakage current.

Keywords: GAA FET, TCAD, NWT, DIBL, SS, Vti etc.

Introduction: With the shrinkage in technology, is increasing. transistor density downscaling of transistors is required. But making transistors smaller leads to degradation in device performance [1]. This degradation is due to dominant short channel effects (SCEs) such as drain induced barrier lowering (DIBL), subthreshold swing (SS), threshold voltage (Vti) etc. Several structures like double gate [2], tri-gate transistors [3] have replaced MOSFETs. After tri-gate, gate all around structures have the advantages of strong electrostatic control of channel by gate [4]. The circular, rectangular and triangular NWTs (TNWT) have been discussed in the literature [5].

Semiconductor NWs are emerged as a powerful materials that can be used in controlled growth and organizations [6], which is making it an evolutionary technology of nano scaled electronics and photonic devices. Inorganic NWs have a higher conducting and higher electrical properties. A NW structure is an object with 1D aspect in which the length to width ratio is greater than 10 and possible width is less than 10 nm. NWs have smallest dimension for efficient exciton and transport of electrons. Electrical conductivity of NW is also affected by structural defect, reduces impurity and its dimensions like cross sectional area, corner effects etc.

**GAA NWFET:** GAA NWFETs are allowed to sustain the relentless progress in CMOS scaling. NWFETs can be formed in high yield with reproducible and repeated electronics properties as required for CMOS technology [7]. Second, the channel diameter can be prepared below 10nm without compromising its electric performance.

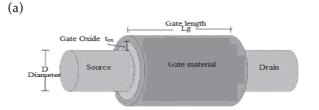

**Figure 1:** (a) Schematic 2D representation of GAA NWFET, (b) Schematic 3D representation of CNWFET.

In addition, the smooth surface, crystalline structure and the ability of axial and radial NW hetrostructures can suppress the charge scattering [8].

**Device design:** In this work, we have designed three different cross section shapes GAA NWT such as triangular [9], trapezoidal and pentagonal cross sections.

**Table I** Architecture parameters of device

| Architecture Parameter                  | Value    |  |

|-----------------------------------------|----------|--|

| Lambda Design Rule(nm)                  | 10       |  |

| Structure orientation                   | <100>    |  |

| Channel Height (nm)                     | 10       |  |

| Channel Diameter (nm)                   | 10       |  |

| Gate oxide(nm)                          | 1        |  |

| Channel length(nm)                      | 20       |  |

| Substrate doping (cm <sup>-3</sup> )    | 2017     |  |

| Source/drain doping (cm <sup>-3</sup> ) | 2.063e20 |  |

| Channel doping(cm <sup>-3</sup> )       | 1615     |  |

Tungsten W (4.5eV) is used for gate terminal, source, drain, metal contacts, HfO<sub>2</sub> (k = 20-25) is used as gate oxide to isolate the channel from gate.

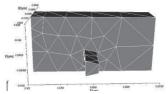

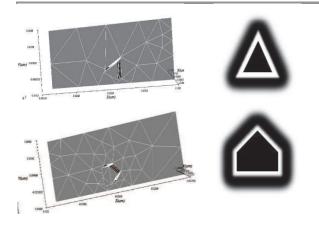

**Figure 2:** Schematic representation of 3-D perspective view and 2-D cross sections.

Two different channel materials Si and Ge are used and a comparative analysis has been done for these devices [10]. The device is designed for different height with a constant channel width 10nm and for different width taking constant height 10nm respectively. Remaining all parameter are common for all devices. Figure 2 shows a 3-D perspective view and 2-D cross section of the channel region of the GAA NWFET. The 3D device structure simulated with Visual TCAD.

**Device Simulations and analysis:** The designed device has been simulated with concentrations given in table 1 at 300k using the classical drift-diffusion approach. All simulations have been done with a range of drain voltage from Vd =0.05-1V. The Threshold voltage (Vti) for all designed NWTs have been extracted from transfer characteristics in active region with drain voltage Vd =0.05V. Ioff current is taken at Vg =0V and drive current (Ion) is taken at Vg =1V with constant drain voltage Vd =0.5V. The DIBL parameter is obtained as the horizontal displacement of I-V characteristics at drain current of 1.0e-7 A and constant drain voltage Vlin=0.05V and Vsat =1.0V. The subthreshold swing is obtained from transfer characteristics.

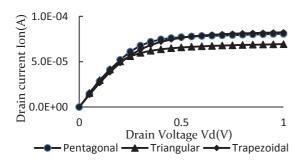

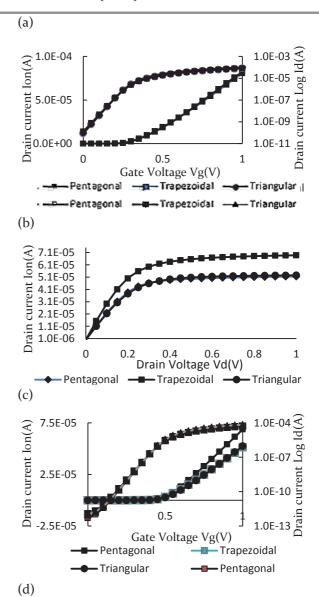

**Figure 3**: (a) Output characteristics plot of SiNWT with different cross sectional shapes (b) Transfer characteristics SiNWT (c) Output characteristics of GeNWT (d) Transfer characteristics of GeNWT.

The output characteristics of GAA NWFET devices have been extracted with varying drain voltage (o-1.oV) at constant gate voltage Vgs=1.oV. The transfer characteristics of GAA NWFET devices have been extracted with varying gate voltage on constant drain voltage Vds=1.oV.

Figure 3 show the relation of Id-Vd and Id-Vg of devices. Figure 3(a) and (c) depict that the drain current is directly proportional to the drain voltage in linear region. Further Id gets saturated w.r.t Vd and it is called saturation region. Trapezoidal NWT (TrNWT) has maximum Ion current as compared to TNWT and Pentagonal NWT (PNWT) because Ion current is directly proportional to cross sectional area. Device with higher cross section area has more conducting area and more charge carriers. TNWT has minimum cross section area thus it shows the minimum Ion current. Figure 3(b) and (d) showed the transfer characteristics of SiNWT and GeNWT

IMRF Journals 14

with different cross sectional areas. Id-Vg plot shows that SiNWT has small Vti than GeNWT.

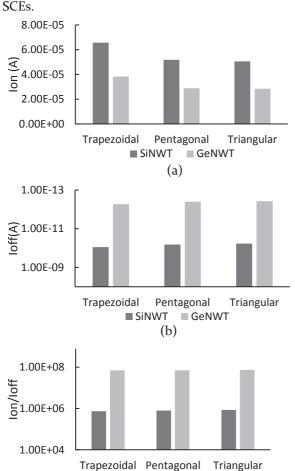

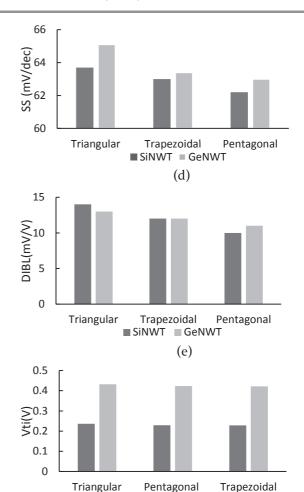

Figure 4(a) shows the TrNWT with Si channel has maximum Ion Current (6.5e-o5). Si has higher DoS as compared to Ge so it shows higher Ion current in short channel designed devices. Figure 4(b) shows the off current of different devices. Off current is a kind of leakage current which flows in the device when voltage is not applied. Ge channel devices have better leakage current than Si channel devices. Figure 4(c) shows the Ion/Ioff ratio of different devices. Ion/Ioff presents the switching speed of devices and it is approximately anti-proportional to the cross section area.

TNWT with Ge channel shows the maximum Ion/Ioff ratio (7.43Eo7) as compared to other devices. Figure 4(d) depicts the SS of GAANWT devices. The minimum value of SS shows the leakages and lower SCFs

■ SiNWT ■ GeNWT

(c)

Figure 4 a comparative analysis of(a) Ion current of SiNWT and GeNWT, (b) Ioff current of SiNWT and GeNWT (c) Ion/Ioff ratio of SiNWT and GeNWT.(d) SS of SiNWT and GeNWT, (e) DIBL of SiNWT and GeNWT and GeNWT and GeNWT.

■ SiNWT ■ GeNWT (f)

Basically SS effects depend upon corner effect, channel length and gate control ability. Thus SiPNWT has minimum SS (62.2mV/dec) and GeTNWT has maximum SS (65.3mV/V). Figure 4(e) shows the DIBL of GAANWT. SiPNWT has minimum DIBL (10mV/V) and SiTrNWT has maximum DIBL (14mV/V).

Figure 4(f) shows the Vti characteristics of GAANWT. Threshold voltage defines the voltage at which the device starts working. Basically short channel devices is used in low power applications and need to have lower threshold voltage. So Si TNWT has maximum Vti (0.2386V) and TrNWT has minimum Vti (0.2285V). Si PNWT Vti (0.2294V) lies in between TNWT and TrNWT. The same relations are hold by GeNWT. Ge TrNWT has minimum Vti (0.4217V).

Table II Simulated results of GAANWT with different cross section shapes and channel materials

**Table II** presents the effects of cross sections shapes and channel materials on Ion and Ion/Ioff ratio of NWT

| Cross<br>Sectio | SS(mV/de<br>c) |      | DIBL(m<br>V/V) |    | Vti(V)     |            |

|-----------------|----------------|------|----------------|----|------------|------------|

| n<br>Shape      | Si             | Ge   | Si             | Ge | Si         | Ge         |

| TNWT            | 63.<br>7       | 65.1 | 14             | 13 | 0.23<br>66 | 0.43<br>17 |

| PNWT            | 63             | 63.4 | 12             | 12 | 0.22<br>94 | 0.42<br>28 |

| TrNW<br>T       | 62.<br>2       | 63   | 10             | 11 | 0.22<br>85 | 0.42<br>17 |

**Table III** Simulated results of GAANWT with different cross section shapes and channel materials

| Cross  | Ion(A) |      | Ioff (A) |      | Ion/Ioff |      |

|--------|--------|------|----------|------|----------|------|

| Sectio | Si     | Ge   | Si       | Ge   | Si       | Ge   |

| n      |        |      |          |      |          |      |

| Shape  |        |      |          |      |          |      |

| TNWT   | 5.05   | 2.84 | 5.9      | 3.82 | 8.5      | 7.4  |

|        | E-05   | E-05 | E-11     | E-13 | 4Ē       | 3Eo  |

|        |        |      |          |      | 05       | 7    |

| PNWT   | 5.18   | 2.88 | 6.5      | 4.02 | 7.8      | 7.16 |

|        | E-05   | E-05 | E-11     | E-13 | Eo5      | Eo7  |

| TrNW   | 6.57   | 3.83 | 8.8      | 5.47 | 7.4      | 7.0  |

| T      | E-05   | E-05 | E-11     | E-13 | Eo5      | Eo7  |

**Table IV** Comparison between different cross section shapes and channel materials

| Parameter |    | PNWT vs TN    | Triangula |          |

|-----------|----|---------------|-----------|----------|

|           |    | TrNWT         |           | r[5]     |

| Ion       | Si | +2.89 %       | than      | +5 times |

|           |    | TNWT          |           |          |

|           |    | -21% than Trl | TWI       |          |

|           | G  | +1.40%        | than      | +3 times |

|           | e  | TNWT          |           |          |

|           |    | -24% than Tr  |           |          |

| Ion/Ioff  | Si | -7.50%        | than      | -4 times |

|           |    | TNWT          |           |          |

|           |    | +6.04%        | than      |          |

|           |    | TrNWT         |           |          |

|           | G  | -3.63%        | than      | 17 times |

|           | e  | TNWT          |           |          |

|           |    | +2.28%        | than      |          |

|           |    | TrNWT         |           |          |

| SS        | Si | -2.35% than T | NWT       | -0.49%   |

## References

- 1. Charis, A. M. (2011), "Fifty Years of Moore's Law", IEEE Transactions on Semiconductor Manufacturing, vol.24, 2, pp. 5-7.

- 2. Chopade, S.S., Mane, S. and Padole, D. (2013), "Design of DG-CNFET for Reduction of Short Channel Effect Over DG MOSFET at 20nm", IEEE

|      |    | -1.26% than      |         |

|------|----|------------------|---------|

|      |    | TrNWT            |         |

|      | G  | -3.22% than TNWT | -1.56%  |

|      | e  | -o.63% than      |         |

|      |    | TrNWT            |         |

| DIBL | Si | -28% than TNWT   | same    |

|      |    | -16% than TrNWT  |         |

|      | G  | -15% than TNWT   | -21%    |

|      | e  | -8.33% than      |         |

|      |    | TrNWT            |         |

| Vti  | Si | -3.04% than      | -26%    |

|      |    | TNWT             |         |

|      |    | +0.39% than      |         |

|      |    | TrNWT            |         |

|      | G  | -2.06% than      | +36.38% |

|      | e  | TNWT             |         |

|      |    | +0.26% than      |         |

|      |    | TrNWT            |         |

Table III shows the variation of SCEs with variation of channel materials and shapes. Table IV presents the Comparison between different cross sections and channel materials. Si TrNWTs have shown maximum Ion current because of maximum conducting area. But due to losses of gate controllability, it has maximum SCEs.

Conclusion: It was found that PNWT can improve the electrical results. PNWTs have better performance in terms of SCEs like SS and DIBL and optimum Ion/loff ratio, whereas Si Trapezoidal NWTs have shown maximum Ion current because of maximum conducting area. But due to losses of gate controllability, it has maximum SCEs. Triangular NWT has good controllability due to the corner effects so it has less SCEs than TrNWTs but due to small cross section area it has minimum Ion current. In this work, Silicon NWTs have better Ion and better SCEs than Ge. But Ge has shown better ion/Ioff Ratio and better leakage current.

Acknowledgment: I am highly grateful to Dr. M. S. Saini, the Director, Guru Nanak Dev Engineering College (GNDEC), Ludhiana, for providing this opportunity to carry out the present work. The constant guidance and encouragement and access to facilities received from the Faculty and staff of Department of Electronics & Communication Engineering, GNDEC, Ludhiana, have been of great help in carrying the present work and is acknowledged with reverential thanks.

- Region Conference (TENCON), Xian China, pp. 1-5.

- 3. Duarte, J., Paydavosi, N., Venugopalan, S., Sachid A. and Hu, C. (2013) "Unified FinFET Compact Model: Modelling Trapezoidal Triple-Gate

IMRF Journals 16

- FinFETs", IEEE Electron Device Letters, vol. 34, 12, pp. 135-138.

- 4. Lokayath Kathi, Subha.D, Assessment Of Lateritic Soil Stabilized With Sand And Coir Mat Geotextile As Pavement Subbase Material.; Engineering Sciences international Research Journal: ISSN 2320-4338 Volume 3 Issue 2 (2015), Pg 77-81

- 5. Chen, X. and Tan, C. M. (2014), "Modeling and analysis of gate-all-around silicon nanowire FET", Microelectronics Reliability, vol. 54, 8, pp. 1103-1108

- 6. Xuan, H., Fan, J., Yang, Y., Zhang, H., Li, M. and Huang, R. (2014), "Performance Studies in Nanowire Field-Effect Transistors with Different Cross Sections", IEEE ICSICT Conference, Guilin, CHINA, pp.1-3.

- A.Senthilrajan, Pest Control In Paddy Using Segmentation In Image Processing.; Engineering Sciences international Research Journal: ISSN 2320-4338 Volume 3 Issue 2 (2015), Pg 82-85

- 8. Zheng, Y., Rivas, C., Lake, R., Boykin, B. and Klimeck, G. (2005), "Electronic Properties of Silicon Nanowires", IEEE Transactions on electron devices, vol. 52, 6, pp. 15-18.

- 9. Gu, J. J., Liu, Y. Q., Wu, Y. Q., Colby, R., Gordon, R. G. and Ye, P. D. (2011), "First Experimental

- Demonstration of Gate-all-around III-V MOSFETs by Top-down Approach", IEDM, vol. 11, 770, pp. 8-12

- 10. Rns Murthy, Allu Revathi Devi, Review On The Maintenance Of The Built Forms From The Seepage Of Water.; Engineering Sciences international Research Journal: ISSN 2320-4338 Volume 3 Issue 2 (2015), Pg 86-88

- 11. Gupta, R., Dass, D., Prasher, R. and Vaid, R. (2014) "Study of Gate all around lnAs/Si based Nanowire FETs using Simulation Approach", IEEE ICSPCT conference, Ajmer, India, pp. 557-560.

- 12. Zhang, Y. B., Xu, H., Wang, Y. and Zhang, S. D. (2014), "Comparative Study of Triangualr-shaped Silicon Nanowire Transistor", IEEE ICSICT Conference, Guilin, CHINA, pp. 5-8.

- 13. Srinivas Daketi, Cultural Approach To Architecture.; Engineering Sciences international Research Journal: ISSN 2320-4338 Volume 3 Issue 2 (2015), Pg 89-92

- 14. Shifren, L., Aitken, R., Brown, A., Chandra, V., Miller, C. (2014) "Predictive Simulation and Benchmarking of Si and Ge pMOS FinFETs for Future CMOS Technology", IEEE Transactions on Electron Devices, vol. 61, 7, pp. 2271-2277.

\*\*\*

Mr. Jaidev/B. Tech (ECE)/RTU KOTA/M. Tech (ECE)/GNDEC/ Ludhiana/ Ms. Navneet Kaur/ Assistant Professor/ Guru Nanak Dev Engineering College/ Ludhiana/ Dr. Sandeep Singh Gill/ Professor and Head (ECE)/Dean/ Guru Nanak Dev Engineering College/ Ludhiana/